목차

SPI 통신이란

SPI(Serial Peripheral Interface)는 I2C, CAN, UART와 같은 시리얼 통신(직렬 통신)방식 중 한 가지다.

마이크로컨트롤러, 시프트 레지스터, SD카드 등의 소형 주변 장치 사이에 데이터를 전송하기 위한 기능이다.

간단하게, 기기와 기기 또는 칩(IC)과 칩 사이에서 데이터를 주고받기 위한 통신방법 중 한 가지이다.

SPI 통신 특징

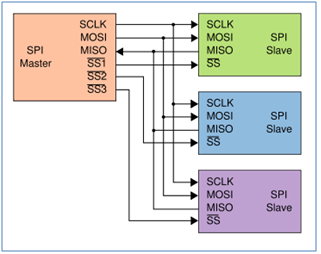

- 1:N 통신을 지원하는 동기식 통신 방식이며, N개의 통신을 하기 위해서 N개 만큼의 선이 필요하다

- 두 개의 Data Bus를 사용하는 전 이중(full duplex)통신이다. $] 전 이중 통신 : 양방향 통신이 가능한 것, ex) 전화

- SPI 프로토콜에 의해, MOSI/MISO 선으로 전송되는 데이터를 SCK 클럭과 동기화하며,CPOL(Clock Polarity)와 CPHA(Clock Phase)로 결정된 SPI 통신의 방법은 총 4가지의 모드가 있다.

- SPI 통신을 하는 IC칩은 이 4가지 모드를 다 지원하는 경우도 있지만, 특정 모드만 지원하는 경우도 이으므로 IC의 데이터시트에서 SPI 모드를 확인해야 된다.

장점

- 전송기가 필요하지 않음,

- 매우 단순한 하드웨어 인터페이스 처리,

- IC 패키지에 4개의 핀만 사용하며 이는 병렬 인터페이스에 비해 수가 적은 것이다.

- 하드웨어 주소 지정된 인터페이스가 단순하기 때문에 전송되는 비트 수에 대한 완전한 유연성 제공된다.

- 동시에 송수신이 가능하다.

- I2C에 비해 속도가 빠르다.

단점

- RS-232, RS-485, CAN 버스보다 비교적 더 짧은 거리에서 동작한다.

- 슬레이브에 의한 하드웨어 흐름 제어가 없다.

- 일반적으로 노이즈 스파이크에 영향을 받는 경향이 있어서 통신 문제를 일으킬 수 있다.

- 하나의 마스터 장치만 지원함

통신방법

1개의 마스터와 N개의 슬레이브 연결

클럭의 구성

SPI 통신을 위한 구성 핀

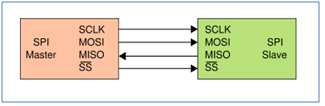

4개의 단자 : MISO, MOSI, SCK, SS

| MOSI | SDI, DI, SI | Master → Slave 방향성이 있는 데이터 선 |

| SLCK | SLK, CLK | 동기화 신호(클록) |

| MISO | SDO, DO, SO | Slave → Master 방향성이 있는 데이터 선 |

| SS | nCS, CS, nSS, STE, CE | 하나의 Master가 다양한 Slave와 통신할 때, 특정 Slave를 선택하는 데이터 선 |

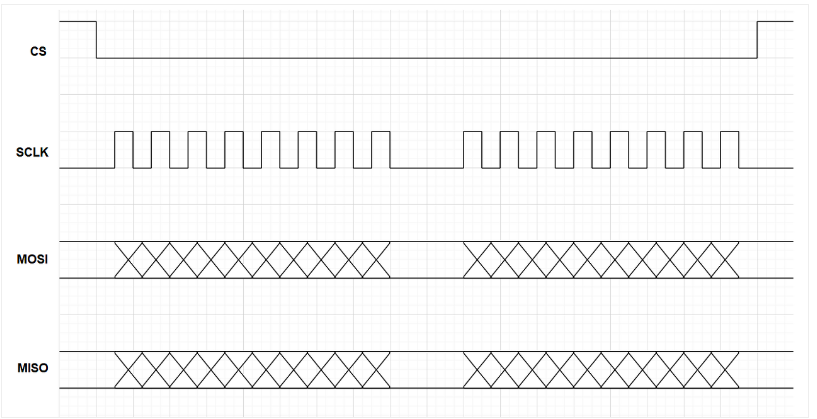

SCLK : 동기화 신호 (CLOCK 신호 통신)

- Serial Clock(직렬 클럭)으로 마스터에서 출력하여 슬레이브로 입력해준다. SPI 통신 주기를 SCLK로 설정할 수 있다.

MOSI : 마스터 출력 → 슬레이브 입력

- Master Output Slave Input, 마스터에서 슬레이브로 데이터를 전송할 때, MOSI를 사용한다.

MISO : 마스터 입력 ← 슬레이브 출력

- Master Input Slave Output, MOSI를 통해 슬레이브에 명령 DATA가 들어오면, MISO를 통해 슬레이브에서 마스터로 응답 DATA가 출력된다.

SS : 슬레이브 장치를 선택하여 통신

- Slave Select, 슬레이브를 선택할 때 사용한다.

중요한 포인트 3개

- IC 칩의 Spec을 보고 통신 대역을 설정해야 함. 다시 말해서 SCK Clock의 속도를 어떻게 정할지 결정해야 함. 예를 들어 IC Chip에서 최대 5MHz까지 통신 대역이 가능하다고 한다면, 5MHz 보다 작거나 같도록 SCK Clock의 속도를 Master에서 조절해야 함.

- IC칩의 Spec을 보고 Polarity를 결정해야 함.

SPI는 Clock Polartiy(CPOL)와 Clock Phase(CPHA)의 조건에 따라 Sampling 위치가 달라짐. - 마지막으로 Delay Time을 Spec에 맞게 설정해야 합니다.

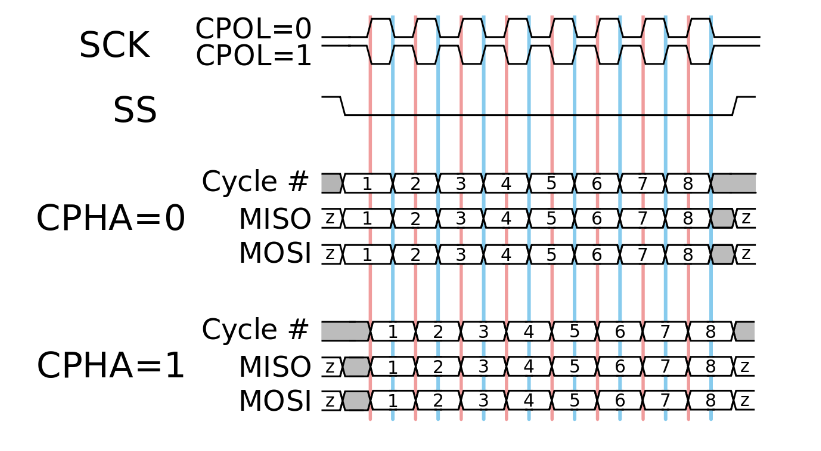

SPI 통신 4개의 모드

CPOL이 0인 경우에는 클럭신호의 기본값이 0(low),

CPOL이 1인 경우에는 클럭신호의 기본값이 1(high)이 됩니다.

CPHA가 0이면 클럭신호의 첫 번째 엣지에서 값을 읽고,

CPHA가 1이면 클럭신호의 두 번째 엣지에서 값을 읽는다는 뜻입니다.

| mode | CPOL | CPHA |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

mode 0, 1

CPOL이 0인 경우, 클럭신호가 발생하지 않을 때 SCK선의 상태가 low입니다. CS핀이 High(Rising edge) -> Low(Falling edge)로 바뀌면 SCK선으로 클럭신호가 전달되고, MOSI/MISO핀의 상태가 high-Z에서 low또는 high상태로 바뀝니다.

CPOL이 1인 경우와 다르게, 클럭신호 주기의 첫 번째 엣지는 상승엣지이고, 두 번째 엣지는 하강엣지입니다.

mode 0 : CPHA가 0이면, master와 slave장치는 클럭신호 주기의 첫 번째 엣지인 상승엣지에서 비트값을 읽고, 하강엣지에서 비트값을 변경할 수 있습니다.

mode 1 : CPHA가 1이면, 이 장치들은 클럭신호 주기의 두 번째 엣지인 하강엣지에서 비트값을 읽습니다. 그리고 비트값은 상승엣지에서 바뀔 수 있습니다.

데이터가 모두 전송되고 CS핀이 high상태로 바뀌면, 클럭신호는 더이상 생기지 않고 MOSI/MISO선은 high-Z 상태가 됩니다.

mode 2, 3

CPOL이 1인 경우, 이때는 클럭신호가 발생하지 않을 때 SCK선의 상태가 high입니다. CS핀이 High(Rising edge) -> Low(Falling edge)로 바뀌면 SCK선으로 클럭신호가 전달되고, MOSI/MISO핀의 상태가 high-Z에서 low또는 high상태로 바뀝니다.

CPOL이 0인 경우와 다르게, 클럭신호 주기의 첫 번째 엣지는 하강엣지이고, 두 번째 엣지는 상승엣지입니다.

mode 2 : CPHA가 0이면, master와 slave장치는 하강엣지에서 비트값을 읽고, 상승엣지에서 비트값을 변경할 수 있습니다.

mode 3 : CPHA가 1이면, 이 장치들은 클럭신호 주기의 두번째 엣지인 상승엣지에서 비트값을 읽습니다. 그리고 비트값은 하강엣지에서 바뀔 수 있어요.

데이터가 모두 전송되고 CS핀이 high상태로 바뀌면, 클럭신호는 더이상 생기지 않고 MOSI/MISO선은 high-Z 상태가 됩니다.

high-z 상태

출력 Z는 출력쪽에 어떤 전압도 드라이브 하지않은 상태이다. 즉, 신호가 없고 뜬 상태이다.

하나의 신호선에 복수의 출력 소자를 연결하는 버스 구조를 사용하는 경우에는 반드시 신호를 출력할 소자와 수신할 소자 하나만 연결해야한다.

회로 제어를 잘못하여 복수의 출력 회로가 동시에 접속되어 버리면 회로 사이에 비정상적인 전류가 흘러서 소자가 파괴될 수도 있다.

이 파괴를 막기 위해서 신호가 출력되지 않는 상태가 되어야 한다.

이 말은 즉, 저항이 아주 높은 상태를 뜻한다. 그렇다고 끊어진 상태는 아니다. 무한대의 저항은 단선을 뜻하는데, 무한대까지는 아니고, High, 즉 높은 저항이라는 뜻입니다. 이와 같이 출력 신호선에서 전기적으로 절연된 상태를 하이 임피던스(High Impedance)라고 부르고, HIGH, LOW 둘 다 아닌 제 3의 상태로 취급되며, 하이 임피던스 상태는 기호로 “Z”라고 표기한다.